NG体育,对于 Chiplet 技术发展趋势进行展望。他表示 Chiplet 技术发展现状暗流涌动,机遇丛生。Chiplet 不是单一技术,而是一系列关键先进技术的有机融合。这是一个战略赛道,我们需要凝聚共识,抓住重大创新机遇。

Chiplet 技术是通向高算力芯片的必经之路,国际领先的高算力芯片都采用了芯粒技术;

算力是数字经济时代的新质生产力。ChatGPT 等 AI 大模型的爆发刺激了对算力的需求,对算力的需求每两个月增加一倍。2023 年 3 月 15 日,OpenAl 发布 ChatGPT-4NG体育平台、具备 1.8 万亿的模型参数,训练需要上万张 Nvidia H100 显卡,计算量约为 2.15e25FLOPS。

传统单片集成算力芯片面临面积墙、存储墙、成本墙、功耗墙等瓶颈,难以持续。吴华强说到:「Chiplet 不是未来时而是现在时。Chiplet 技术是通向高算力芯片的必经之路。」

国际领先的高算力芯片都采用了芯粒技术。如英伟达发布 B200 GPU,在算力上实现巨大的代际飞跃基于台积电的 N4P 制程工艺,晶体管数量达到了 2080 亿个,配备 192GB HBM3e 内存。

AI 时代 Chiplet 市场规模正在加速扩张。全球已经安装了价值约 1 万亿美元的数据中心,而这个上万亿美元的数据中心市场正在从通用计算向加速计算和生成式人工智能转型,一个新的计算时代已经开启。

与此同时,Chiplet 技术的应用领域也在逐渐扩大。Chiplet 技术继 GPU 等云端高算力芯片之后,在桌面市场的 AIPC(CPU+AI)领域显示出其价值。AMD 在 Computex2024 大会上发布了当时世界上最快的桌面 CPU 芯片 HR9 9950X 采用了 Chiplet 技术;英特尔公布下一代面向 AI PC 的移动处理器 Lunar Lake,将会混合封装台积电 N3B 工艺和自家 Intel18A 工艺的芯粒。

吴华强表示,Chiplet 不是单一技术,而是一系列关键先进技术的有机融合,形成了涵盖从顶层架构到底层器件的全新技术体系。从上图中可以看到,包括了接口标准与生态、互联技术、电源技术、计算体系架构、存储技术、先进封装集成等技术NG体育平台。

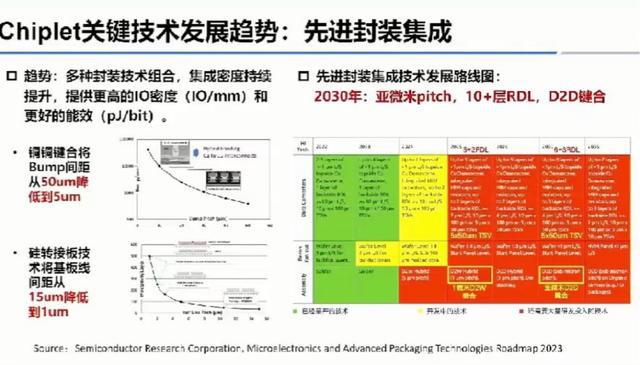

多种封装技术组合,集成密度持续提升,提供更高的 IO 密度(IO/mm)和更好的能效(pJ/bit)。比如铜铜键合将 Bump 间距从 50um 降低到 5um;硅转接板技术将基板线um,密度大幅度提升。先进封装集成技术发展路线 年能够达到:亚微米 pitch、10+层 RDL、D2D 键合。因此这个领域将来对于设备材料都有很多创新,孕育了许多新机会。

从封装技术来看,扇出型封装,无 TSV 结构的工艺,制造成本低封装体厚度小。硅桥技术非常重要,英特尔的封装基板硅桥和台积电的扇出型硅桥,使用小尺寸硅桥替代大面积硅转接板实现芯片间高密度、高带宽互连,总制造成本降低、硅工艺复杂性降低,集成复杂性增大。

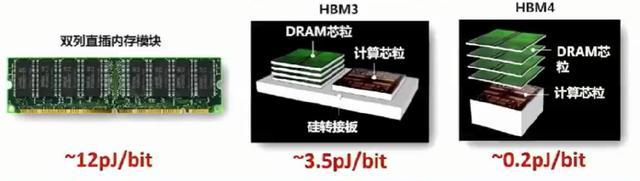

存储在 Chiplet 发展中绕不开的话题。吴华强表示,Chiplet 关键技术发展另一趋势是存储技术(HBM)。先进封装集成技术带来更高的存储密度、带宽和更高的能效。

以前双列直插内存模块,传输能效是 12pJ/bit,到了 HBM3 可以达到 3.5pJ/bit,未来正在规划中的 HBM4 能效更是能够达到 0.2pJ/bit,再降一个数量级。今年 9 月,台积电与三星宣布合作研发新一代无缓存 HBM4 内存技术,用于高算力 AI 芯片无缓存 HBM4 技术将会在现有 HBM4 内存上提升 40% 的能效,降低 10% 的延时。

同时,存储技术方面存算一体也孕育而生。存内计算(Processing-in-memory,PIM)PIM-HBM 架构,将处理单元嵌入 HBM 的逻辑库中,以减少互连的能耗和延迟,可以实现较低的 DRAM 访问成本。

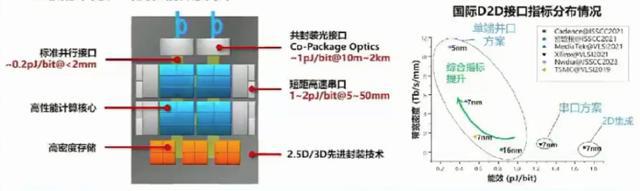

互联技术的趋势是短距、长距、串口、并口、电口、光口等多种互联技术体制融合,满足全场景芯粒互联的带宽、密度和能效要求。

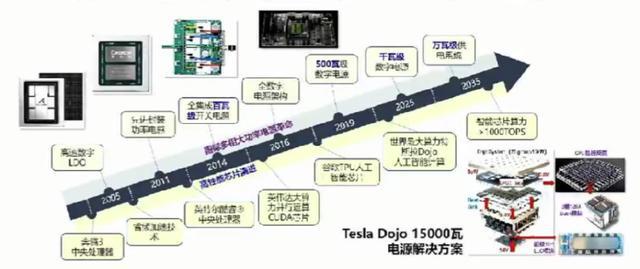

电源技术的趋势则是,传统功率转换架构无法应对高性能计算芯粒的严峻挑战,「功率即性能」。功率是性能,电压不稳定会对计算产生很大影响。分布式功率器件集群创新架构、分布式多场管理技术、快速电源响应技术具备巨大潜力。Chiplet 开辟了许多技术创新之路。

计算架构的发展趋势是可扩展的异构架构、标准化接口,朝适应于 Chiplet 技术的计算体系架构演进。而且计算体系架构的分析需要专门的仿真模拟工具NG体育平台,没有这样的工具很难分析整个系统的性能。

英特尔的异构芯粒处理器,采用一种「新型柔性拼接架构」,由四个异构芯粒(GPU 块,SoC 块NG体育平台、IO 块和 CPU 块)通过一个 basedie 连接而成。实现了可扩展的异构处理器系统框架,标准化的接口,但是仅能做到对固定功能单元的参数化扩展。

AMD 的混合封装高算力 AI 芯片,按照:4 个 lO die+8 个计算 die+HBM3,3D 混合键合+2.5D 硅转接板的封装,实现了可扩展的多芯粒(同构)集成方案,以 IOD 为枢纽和扩展接口。吴华强说到:「英特尔和 AMD 的架构体系与英伟达有所不同,这非常有意思。大型玩家开始采用不同的技术路线。」

这方面的趋势在于,芯粒标准再进化,UCle 各级成员不断推出基于其标准的产品,生态建设进展迅速。

标准方面,8 月 6 日,UCle 联盟发布 2.0 规范,包含以下亮点:全面支持具有多个芯片的任何系统级封装(SiP)结构的可管理性、调试和测试;支持 3D 封装,显著提升带宽密度和功率效率;改进的系统级解决方案,其可管理性被定义为芯片堆栈的一部分;针对互操作性和合规性测试优化的封装设计;完全向后兼容 UCle 1.1 和 UCle 1.0。近日,AMD、博通、思科等八家公司宣布为人工智能数据中心的网络制定新的互联技术开放标准 UALink(UltAccelerator Link)以打破 Nvidia 的垄断。

多个国家和地区在 Chiplet 技术上的竞争将愈演愈烈。美国国家半导体技术中心(NSTC)发布《战略蓝图》,建立 Chiplet 计划,以实现开放创新的 Chiplet 市场英特尔牵头成立 UCle 联盟,推动 Chiplet 技术标准化、生态化。

韩国三星提出高级代工生态系统(SAFE),与合作伙伴建立合作生态系统,实现「一站式 Chiplet 封装」,开发 2.5D/3D 先进封参考设计流程。

中国台积电发起 3D Fabric 联盟,联合产业上下游企业提供全流程的服务,定义 PDK 和接口标准、参考设计流程。

总而言之,Chiplet 技术发展现状是暗流涌动,机遇丛生NG体育平台。Chiplet 技术将在先进封装集成、互联接口、存储技术、电源技术、计算体系架构、接口标准与生态等方面持续创新,不断自我迭代,推动芯片算力持续提升。

吴华强说到:「Chiplet 是一个战略赛道,我们需要凝聚共识,抓住重大创新机遇。」